计算机组成原理2010年4月真题试题及答案解析(02318)

-

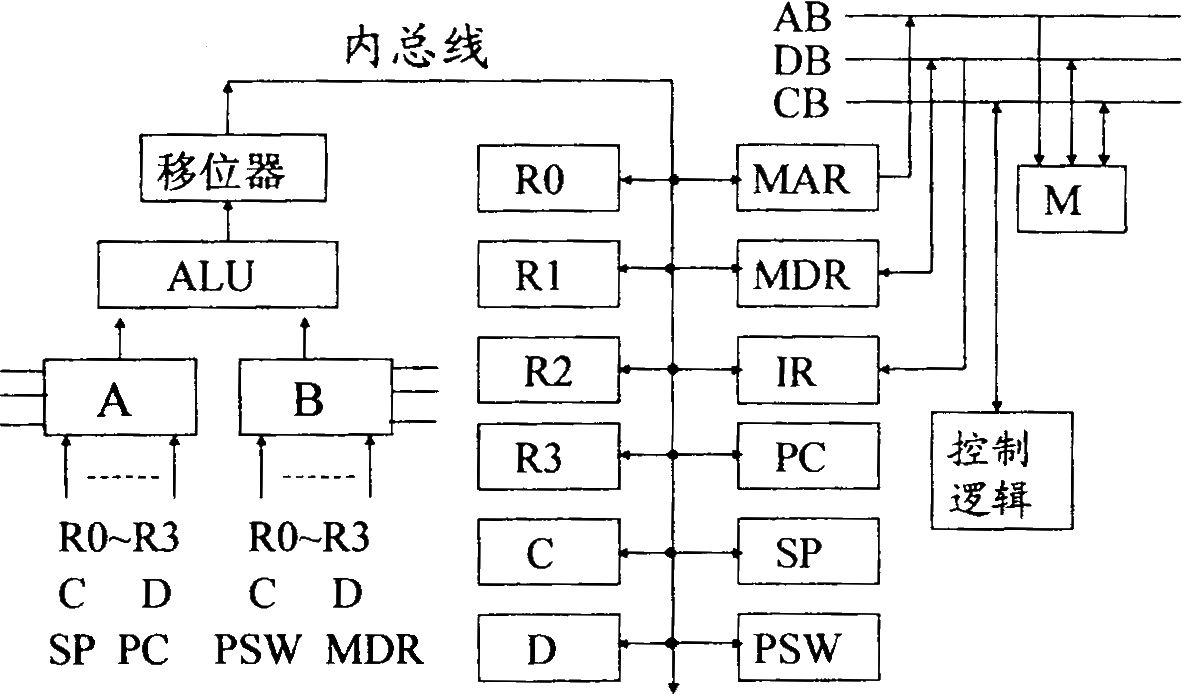

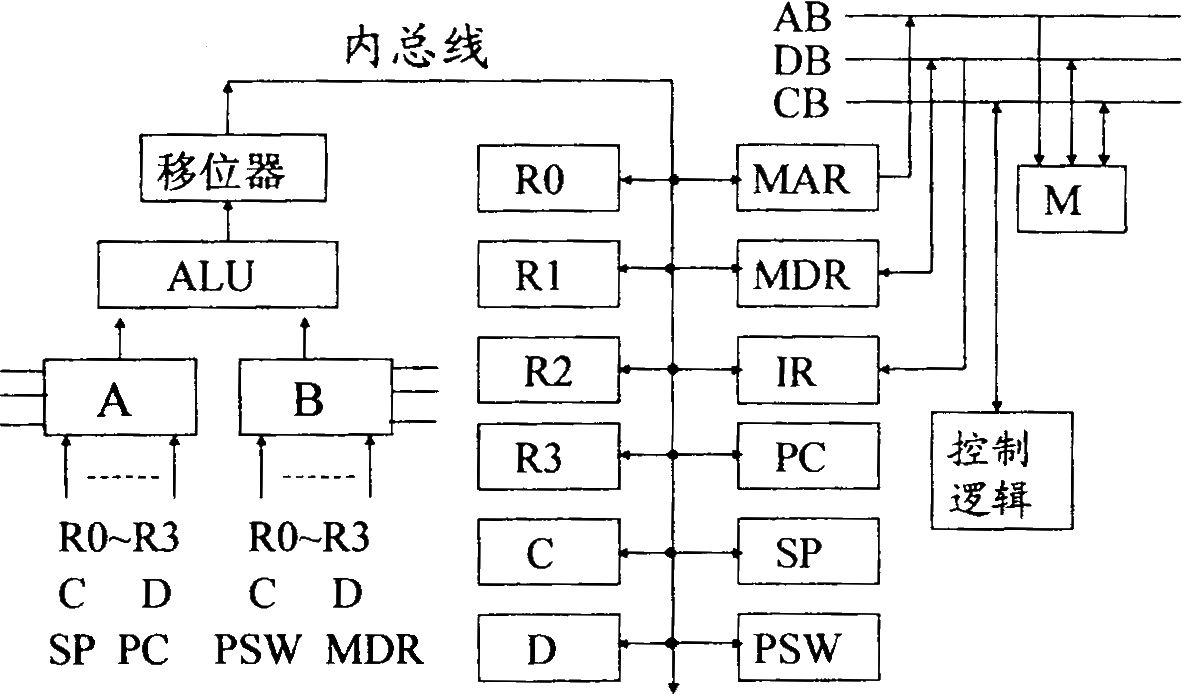

设有计算机的CPU数据通路及其与存储器的连接结构如下图所示,其中,R0~R3为通用寄存器,IR为指令寄存器,PC为程序计数器,SP为堆栈指针,C和D为暂存器,MAR为存储器地址寄存器,MDR为存储器数据缓冲寄存器。

试写出转移指令ADD(R3),(R0)的执行流程。

注:指令功能为加法操作,(R3)和(R0)分别为采用寄存器间接寻址的源操作数和目的操作数。

-

用4K×1位/片的存储芯片构成32KB存储器,地址线为A15(高)~A0(低)

(1)需要几片这种存储芯片?

(2)32KB存储器需要哪几位地址寻址?

(3)在这些地址线中,加至各芯片的地址线是哪几位?

(4)用于产生片选信号的地址线是哪几位(译码法)?

-

用Booth算法计算7×(-4)的4位补码乘法运算,要求写出其运算过程。

-

若CPU中寄存器内容如下,现指令中给出寄存器与其单元内容之间对应关系如下,按寄存器R1间接寻址方式读取的操作数是什么?

寄存器 内容 单元地址 存储内容

R0 1000H 1000H 3A00H

R1 3A00H 2000H 1000H

R2 2000H 3A00H 2000H

R3 3C00H 3C00H 3C00H

-

中断的过程与子程序调用的区别是什么?

-

CPU主要有哪些基本功能?CPU主要由哪些基本部件构成?

-

总线上有哪些信息传输方式?各有哪些特点?

-

RAM与ROM有何异同?

-

什么是指令格式?计算机指令为什么要有一定的格式?

-

RAM

-

显示器分辨率

-

指令系统

-

中断屏蔽字的作用是( )

- A.暂停外设对主存的访问

- B.暂停对某些中断的响应

- C.暂停对一切中断的响应

- D.暂停CPU对主存的访问

-

在CPU中,指令寄存器IR用来存放( )

- A.正在执行的指令

- B.即将执行的指令

- C.已执行的指令

- D.指令地址

-

外部设备接口是指( )

- A.CPU与系统总线之间的逻辑部件

- B.系统总线与外部设备之间的逻辑部件

- C.主存与外围设备之间的逻辑部件

- D.运算器与外围设备之间的逻辑部件

-

在磁盘中实现输入输出数据传送的方式( )

- A.只采取程序查询等待方式

- B.只采取程序中断方式

- C.只采取DMA方式

- D.既有DMA方式,也有中断方式

-

采用异步控制的目的是( )

- A.提高执行速度

- B.简化控制时序

- C.降低控制器成本

- D.支持微程序控制方式

-

CPU可直接访问的存储器是( )

- A.硬盘

- B.软盘

- C.光盘

- D.高速缓存

-

采用微序控制的主要目的是( )

- A.提高速度

- B.简化控制器设计与结构

- C.使功能很简单的控制器能降低成本

- D.不再需要机器语言

-

下列寻址方式中,执行速度最快的是( )

- A.寄存器寻址

- B.相对寻址

- C.直接寻址

- D.存储器间接寻址

-

在存储器堆栈结构中,在栈底为最大地址的堆栈操作中压栈是指( )

- A.先使SP减1,再将数据存入SP所指单元

- B.先使SP加1,再将数据存入SP所指单元

- C.先将数据存入SP所指单元,再将SP减l

- D.先将数据存入SP所指单元,再将SP加1

-

在磁盘数据记录方式中,用改进调频制记录数据“1”时,在位单元中间电流的变化是( )

- A.从负值变到正值

- B.从正值变到负值

- C.从负值变到正值或从正值变到负值

- D.保持不变

-

存取速度最快的存储器是( )

- A.主存

- B.硬盘

- C.高速缓存

- D.光盘

-

若地址总线为A15(高位)~A0(低位),若用4KB的存储芯片组成8KB存储器,则加在各存储芯片上的地址线是( )

- A.A11~A0

- B.A10~A0

- C.A9~A0

- D.A8~A0

-

n+l位定点小数的反码表示范围是( )

- A.-1+2-n≤X≤1-2-n

- B.-2n+1≤X≤2n-1

- C.-1-2n≤X≤1+2n

- D.-2n≤X≤-2n+1

-

若十进制数为-49,则其对应的补码[X]补为( )

- A.11100011

- B.11111001

- C.11001111

- D.11001110

-

若十进制数为101,则其对应的二进制数为( )

- A.01100101

- B.01010011

- C.01110001

- D.01010010